在Fan-in和Fan-out晶圆级封装方面有着7年多工作经验的Debbie,自从2018年加入ERS electronic公司以来,不断推动ERS翘曲矫正热拆键合设备的开发。最近我们对她进行了一次专访,希望她可以谈谈当初选择半导体行业的原因、ERS与新加坡微电子研究所(IME)的研究项目,以及对扇出型先进封装领域的展望。

问:你是如何开始在半导体行业工作的?又是什么吸引你涉足扇出型封装领域?

Debbie:我的半导体职业生涯起始于一家位于菲律宾的初创公司。不过早在大学取得物理学位的过程中就已经对半导体有所研究了。因此,当我听说他们想要雇佣有我这样教育背景的人时,便毫不犹豫抓住了机会,成为了公司的一员。供职于这家初创公司期间,我参与了晶圆级芯片封装(CSP)工艺的开发,对我来说这个工作很有趣。后来,公司推出了扇出工艺,这不仅解决了传统CSP的局限性,还提供了更多的灵活性,例如在一个封装中添加不同类型的芯片。扇出的应用领域多种多样,如果你需要SiP, 2.5D或是3D集成,扇出都是可以实现的。这也正是这项技术吸引我的地方。

问:半导体行业的一些大公司也被扇出的种种优势所吸引,使用率正在稳步增长。那么它受欢迎的应用有哪些?

Debbie:对于单芯片来说,扇出技术主要用于CODECs、电源管理芯片(PMICs),以及汽车领域,例如雷达。对于多芯片配置,有逻辑存储,或是传感器和ASIC的组合。另外在射频应用领域,扇出也获得广泛的应用,也是目前备受瞩目的课题。

问:不过,扇出型封装技术仍然存在一些挑战。应该如何应对呢?

Debbie:传统eWLB扇出工艺通常会遇到两个问题:晶粒偏移与翘曲。晶粒偏移是一个普遍存在的问题,对良率影响很大。当晶粒偏移的位置偏离预先设定位置一段特定距离时,这种情况就会发生。这通常是由放置晶粒时的精确程度和模制过程模具的移动造成的。如果是系统性的模具移动是能够得到补偿的,不过在贴膜过程中,晶粒偏移很大程度上是由机器精度决定的。因此,为了降低晶粒偏移,高精度键合是必不可少的,不过价格太过昂贵。

而翘曲则是由于硅与环氧树脂模塑料(EMC)之间的热膨胀系数(CTE)不匹配引起的。在生产过程中,这会引发一是良率,二是操作上的问题,这意味着将无法进行下一步的工艺流程。无论是在晶圆上加载一个分布层,或是后续的特定温度处理,都会影响晶圆的翘曲程度,而机器是无法处理这些不同程度的翘曲的。这就意味着你需要重新设计机器的传输系统、操作系统以及末端执行器来容纳这些不同程度的翘曲。

事实上,这是一个生产工艺流程的问题。它不仅需要操作者对机器进行干预,翘曲的存在还同时增加了设备出错的风险,最典型的要属温度卡盘和末端执行器的真空吸附故障。另外,翘曲还会影响光刻工艺流程。如果晶圆没有被平整的放置在卡盘上,就会出现浮渣,从而造成晶圆外缘芯片短路,最终导致良率的降低。

问:自从三年前你加入ERS,就一直带领团队研发带有翘曲矫正技术的机器。那么ERS是如何应对你刚才提到的种种挑战的?

Debbie:我和我的团队已经开发了晶圆级全自动热拆键合机器ADM330 (Automatic Debonding Machine 330)。采用ERS三温滑动技术,可以将拆键合过程中由于操作引起的翘曲降至最低。热拆键合是建立分布层工艺流程里面的第一步。如果以eWLB为例,翘曲接下来会影响的便是光刻工艺。如果没有把翘曲降到最低,除了会引起操作上的问题,还会影响良率。近期,在与新加坡微电子研究所(IME)合作的研究项目中,我们已经将这项三温滑动技术扩展到了不同的FOWLP布局。

问:可不可以具体介绍一下与IME的合作?

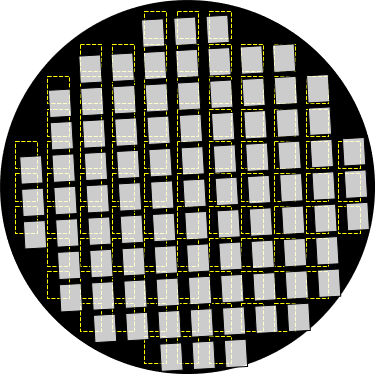

Debbie:与IME合作的项目致力于降低扇出率为1.6时的翘曲。根据一些客户的反馈,在扇出率为1.6时,翘曲可以达到2-3mm。IME帮助我们深入研究温度与翘曲的关系,更关键的是如何应用到ERS的机器中。我们知道,晶圆中硅的密度对翘曲的影响巨大。封装区域离芯片区域越近,可控的化合物材料越少,翘曲度变大的趋势就会越明显。通过使用IME建立的实验样本,结合ERS的“Shock & Lock”技术,我们最终在扇出率为1.6时,实现了小于1.5mm的翘曲度。

问:作为半导体产业十分重要的一个环节,要跟上科技的发展速度,先进封装技术必须要不断突破极限。现如今人工智能、5G、物联网盛行,扇出封装在这其中又扮演了什么样的角色?

Debbie:凭借高密度I/O、良好的电气性能等特点,扇出逐渐成为应对2.5D/3D堆栈、Chiplets……的理想技术。三星、英特尔等公司已经开始探索Chiplets领域,扇出型封装技术也为他们提供了颇具竞争力的解决方案。

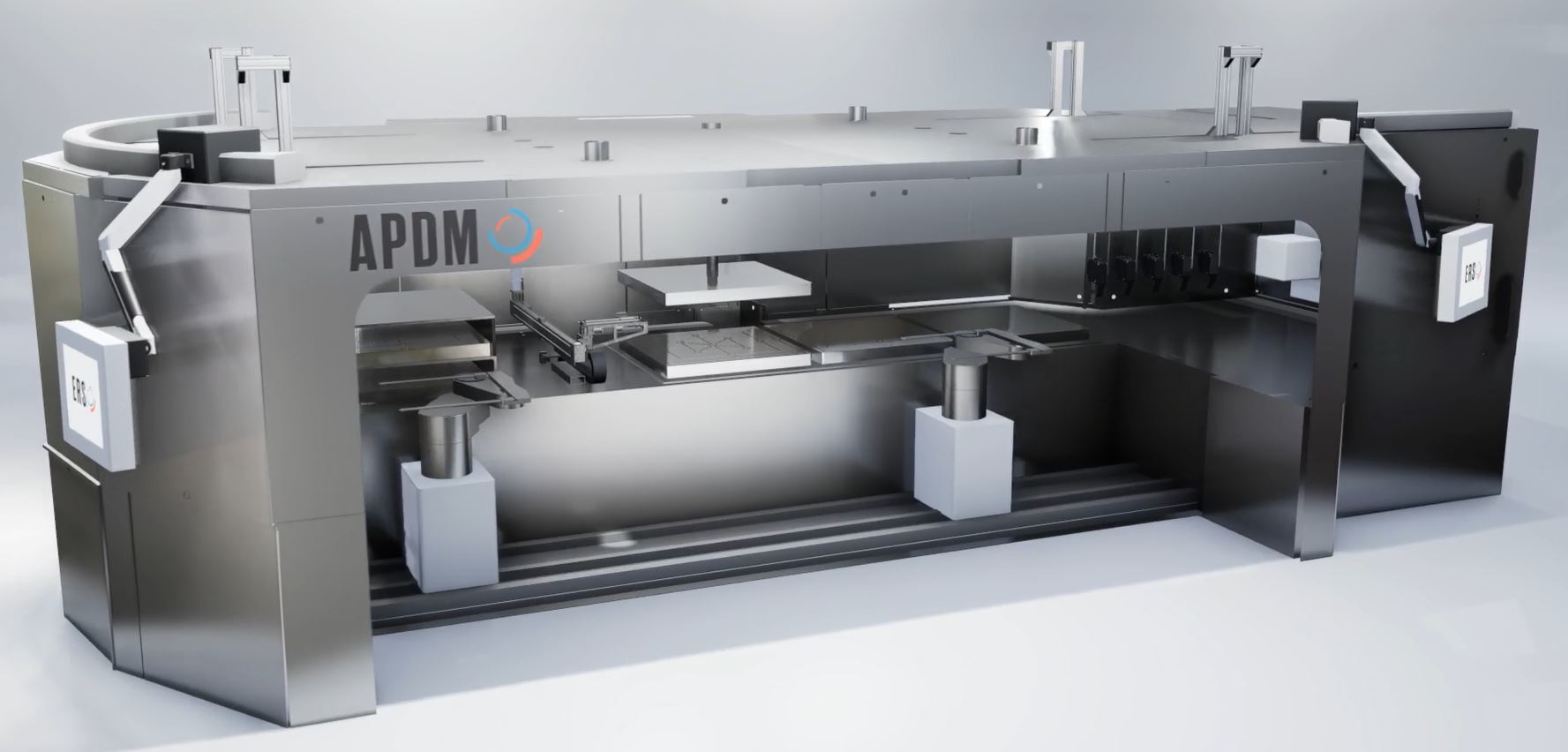

我们也看到越来越多的业界同行开始涉足扇出型封装工艺。对于ERS来说,我们正在为更大的FOWLP布局研发解决方案,另外,针对多芯片、其它类型SiP等更复杂的扇出,不断加强我们的翘曲矫正技术。与此同时,ERS也为面板级封装FOPLP做好了准备。2018年,我们推出了第一台手动面板级热拆键合机,最大可以处理650mmx550mm的面板。该机器的全自动版本APDM正在研发中,预计将于今年年底面世。

如果您想了解更多关于晶圆温度测试的技术信息,请点击这里联系我们。

或是扫描下方二维码,关注“ERS亚洲”获取新鲜资讯。