# **Advanced Packaging Equipment Solutions**

Maximizing yield with advanced semiconductor equipment

#### **About Us**

ERS electronic GmbH is an award-winning provider of state-of-the-art equipment for Advanced Packaging that addresses and solves issues commonly occurring in the semiconductor packaging process. ERS has almost 15 years of experience in providing solutions for thermal debonding and warpage adjustment for Fan-out Wafer-level Packaging (FOWLP) and Panel-level Packaging (FOPLP). Our flagship machine, the ADM330, performs fully automated thermal debonding, leaving no tape residue on the reconstituted wafer. The machine features in-situ warpage adjustment, which is powered by ERS's proprietary technologies, the AirCushion contactless transport method and TriTemp slide, that ensure no handling-induced warpage post-debond.

These capabilities are crucial to avoiding downstream process and production issues and reduced yield. ERS's machines are available as fully automatic, semi-automatic, and manual systems for wafers up to 330 mm and panels up to  $650 \times 650 \text{ mm}$  to meet the wide variety of format requirements in the industry. They can be found on the production floors of most semiconductor manufacturers and OSATs, as well as research institutes worldwide.

2009

ADM200 Shipment of 1<sup>st</sup> Automatic 200mm System

2011

**ADM330** Shipment of 1<sup>st</sup> Automatic 300mm System

2018

**MPDM**Shipment of 1st Manual

Panel Level System

2021

APDM650 Announcement of Automatic Panel Level System

## TriTemp with AirCushion Transport Technology

Addressing Warpage Issues in Wafer Level Packaging

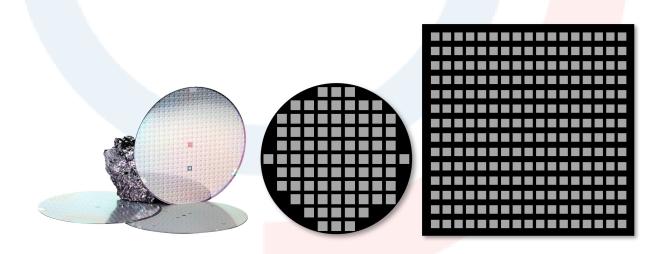

In the context of increasingly complex wafer level packaging, one of the key challenges faced during production is wafer warpage. Warpage refers to the deformation of wafers caused by various factors. This issue significantly hampers the seamless high-volume manufacturing process.

To combat this problem, ERS has developed the TriTemp slide with AirCushion transport technology. This innovative

solution focuses on tackling the warpage issue by implementing a three-stage thermal treatment approach to control the flatness of wafers. By subjecting the wafers to precise thermal conditions at different stages, TriTemp ensures enhanced control over the wafer's flatness, thereby mitigating warpage concerns.

Moreover, TriTemp incorporates the patented AirCushion technology for wafer transport, offering a distinct advantage in eliminating warpage caused by improper handling. By utilizing AirCushion as a gentle and effective means of wafer transportation, the TriTemp system minimizes the introduction of warpage during the manufacturing process.

# **ERS** Equipment Applications

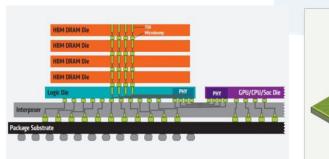

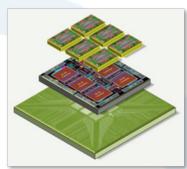

Advanced Packaging for AI, HPC, HBM, SiP and other Heterogeneous Integration

Wafer Level and Panel Level Packaging

## FOWLP Thermal Debond

- Highest temperature uniformity thermal debonder for Fan-Out Wafer Level Packaging.

- A fully automatic system with high throughput, maximum yield, and no consumables.

- Equipped with ERS's patented technology, each thermal debond system is capable of

- multifunctional debonding and warpage adjustment processes.

# Applications

Designed for different Fan-Out technologies utilizing thermal release tape, i.e. eWLB for Core Fan-out and M-Series for High-Density FO (HDFO) and Ultra High-Density FO (UHDFO).

| Wafer Sizes           | 200mm, 300mm                           |

|-----------------------|----------------------------------------|

| Variant               | Manual, semi- and fully-automatic      |

| Factory Communication | SECSII/GEM, GEM300, and OHT compatible |

# FOWLP Warpage Adjust

- Machine is designed to adjust warpage, ensuring smooth processing throughout the

production line.

- WAT's key feature is its contactless transport system, which allows wafer transfer from

- chuck to chuck without losing thermal energy, resulting in the highest processing yield and exceptional warpage reduction performance.

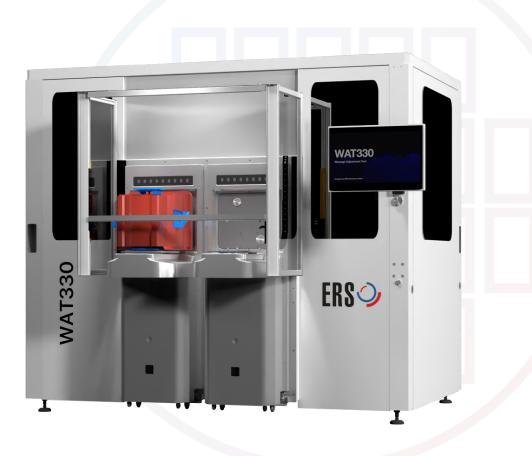

- Its fully automatic machine WAT330 also includes warpage inspection capabilities to manage both pre- and post-adjustment information.

# **Application**

Designed for stand-alone molded wafers.

| Wafer Sizes           | 200mm, 300mm                           |

|-----------------------|----------------------------------------|

| Variant               | Manual, and fully-automatic            |

| Factory Communication | SECSII/GEM, GEM300, and OHT compatible |

## FOPLP Thermal Debond

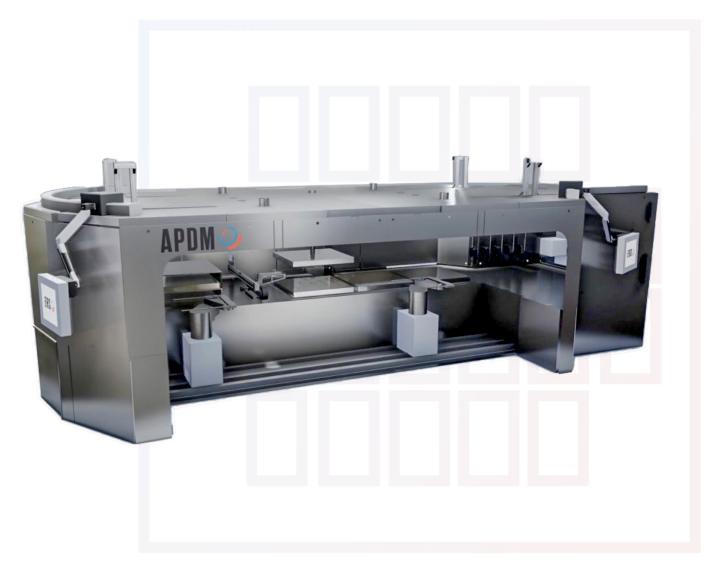

- Panel-level thermal debond system is capable of handling panels up to 650mm x 650mm.

- Thermal debonding is a robust and cost-effective process for ensuring the safe separation of

- the panel from the carrier using thermal release technology.

- The system is extendable with several add-on options, including multi-location laser marking

- and warpage inspection.

- Several technologies utilize panel-level processing, including eWLB Core FO and M-Series HDFO.

# Application

- Designed for Chip-First: Face-down (e.g. eWLB), Face-up (e.g. M-Series); Chip-Last:

- Face-down

| Panel Size            | Up to 650mm x 650mm                    |

|-----------------------|----------------------------------------|

| Variant               | Semi- and fully-automatic              |

| Factory Communication | SECSII/GEM, GEM300, and OHT compatible |

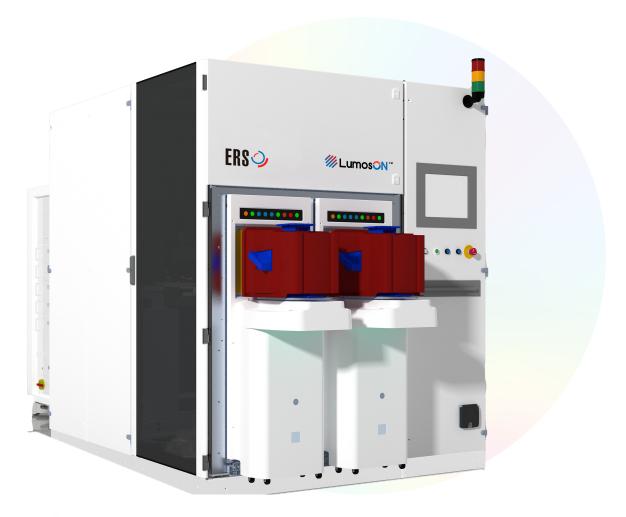

# **<b>#** Lumos<sup>©</sup>N<sup>™</sup> - PhotoThermal Debond

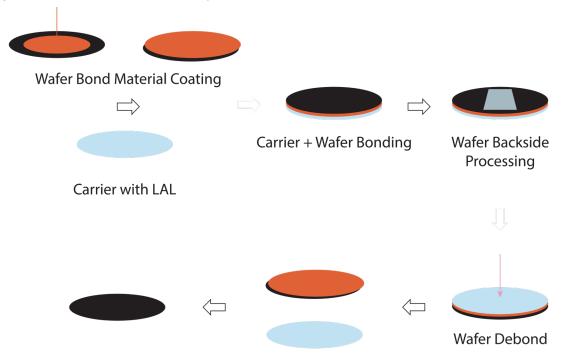

Temporary bonding and debonding processes are vital in semiconductor packaging for both wafer thinning and fan-out technologies. They enable the manipulation of thin wafers during fabrication, ensuring structural integrity and facilitating advanced packaging techniques. Temporary bonding supports the handling of ultra-thin wafers during thinning processes, while also holding redistributed chips in place during fan-out packaging. In addition to facilitating the handling and manipulation of thin wafers, wafer debonding is particularly critical as it allows for the separation of the carrier substrate from the thinned wafer or redistributed chips, enabling the finalization of the packaging process. This step is essential for achieving the desired package thickness, ensuring optimal electrical performance, and enabling further downstream processing steps such as redistribution layer formation and solder ball attachment.

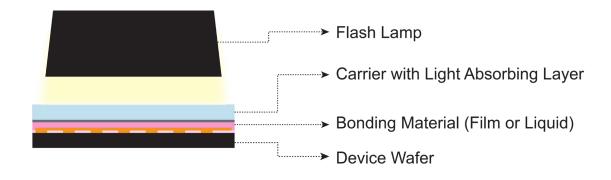

PhotoThermal process allows stress free debonding of temporary bonded wafers from a carrier. Stress free debonding is made possible with a unique process and carrier combination approach. The energy is delivered by a flash lamp with the light absorbed by a light absorbing layer (LAL) in the carrier which converts light energy to thermal. This eliminates the adhesive material attached to the LAL and debonds the wafer safety. These processes enhance yield, throughput, and flexibility in packaging design, ultimately driving innovation in the semiconductor industry.

## PhotoThermal Product Line

- The LumosON™ product line is designed for Temporary Bonding and Debonding processes, reducing costs and increasing flexibility across adhesive types.

- Using a controlled flash lamp (200 nm–1100 nm, up to 45 kW/cm²), it converts light to heat for smooth, stress-free separation of carrier and substrate—minimizing wafer breakage, boosting

- yield, and cutting costs by up to 30% compared to laser debonding.

# Applications

LumosON™ can be utilized across various technologies, including M-Series for HDFO and UHDFO, InFO, CoWoS®, Through Silicon Via (TSV), High Bandwidth Memory (HBM), stacking, and wafer thinning (SiC, GaN).

| Wafer/Panel Sizes  | 200mm, 300mm wafer and panel level up to 600mm x 600mm |

|--------------------|--------------------------------------------------------|

| Variant            | Semi- and fully-automatic                              |

| Factory Automation | SECSII/GEM, GEM300, and OHT compatible                 |

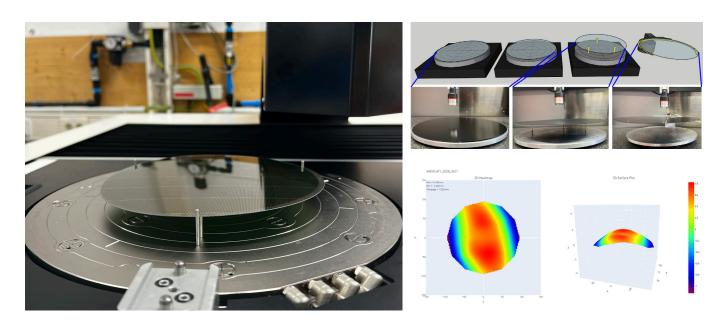

#### Wafer Profiler

The use of a 3D wafer profiler to measure warpage across individual wafers is a critical step in advanced packaging techniques such as Fan-Out Wafer-Level Packaging (FOWLP) and 3D stacking. The ability to accurately profile the warpage of each wafer offers several important advantages that directly impact the manufacturing process, yield rates, and product reliability.

## Measuring Wafer Warpage with a 3D Wafer Profiler

- Enhanced Process Control: Each wafer can exhibit unique characteristics due to slight variations in processing, material properties, and handling.

- Optimized Material Handling and Storage: Understanding wafer warpage helps in optimizing the handling and storage conditions to prevent further warpage or damage.

- Yield Optimization: Significant warpage can lead to process challenges such as poor lithography

alignment, incomplete etching which all reduce yield. By profiling the warpage, manufacturers can

identify wafers that exceed acceptable limits and treat them accordingly

- Feedback for Continuous Improvement: The data collected by the 3D wafer profiler provides valuable feedback that can be used to continuously improve processes.

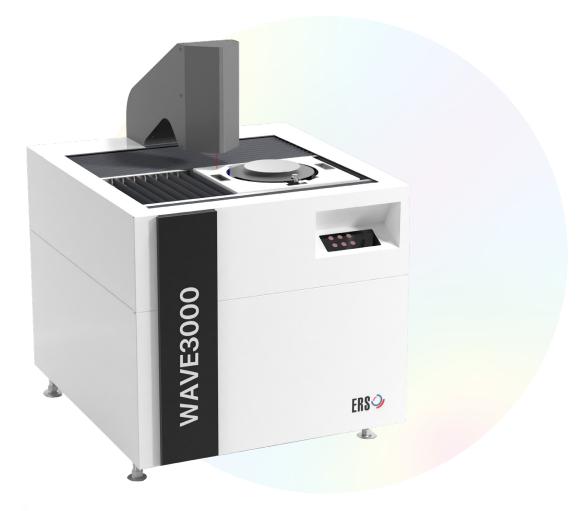

## 3D Wafer Profiler

- Wave3000

- Multi-function measurement machine that can measure warpage, bow and wafer thickness

- High throughput system with measurement in less than 1 minute

- Measures different wafer surface and material from silicon to mold and others

- Flexible platform allowing user to understand warpage behavior on different stages

| Wafer Sizes                     | 200mm, 300mm                                                                                                                          |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| Wafer Surface                   | All surfaces*                                                                                                                         |

| Measurement Types               | Bow, warp, and wafer thickness                                                                                                        |

| Accuracy**                      | 5µm                                                                                                                                   |

| Repeatability   Resolution      | 5μm   1μm                                                                                                                             |

| Heating Capability   Uniformity | 20-250°C   ±2°C (controlled)                                                                                                          |

| Stage Options                   | <ul> <li>Flat-surface free standing</li> <li>Flat-surface vacuumed</li> <li>3-pin position</li> <li>End-effector placement</li> </ul> |

| Measurement speed               | <1 minute per wafer                                                                                                                   |

<sup>\*</sup>E.g. silicon, mold compound, and others

<sup>\*\*</sup>Depending on sensor selection and warpage level

## **CONTACT US**

To request a quotation, please visit: www.ers-gmbh.com

## Headquarters

ERS electronic GmbH Stettiner Str.3+5 82110 Germering/Munich, Germany info@ers-gmbh.de

## **ERS Barbing**

Barbing, Germany Liebigstraße 1, 93092 Barbing/Regensburg, Germany barbing@ers-gmbh.de

#### **ERS Americas**

Dallas, TX, USA +1 214 686 0053 krafthoefer@ers-gmbh.de

#### **ERS Taiwan**

Zhubei, Taiwan +886 972 077 305 perino@ers-gmbh.de

## **ERS China**

Shanghai, China +86 21 5999 1200 zhang@ers-gmbh.de